目录

- 1、前言

- 2、我这里已有的UDP方案

- 3、详细设计方案

- 本 10G-UDP 协议栈功能和性能描述

- 本 10G-UDP 协议栈设计框图

- 用户发送AXIS接口描述

- 用户接收AXIS接口描述

- 控制接口描述

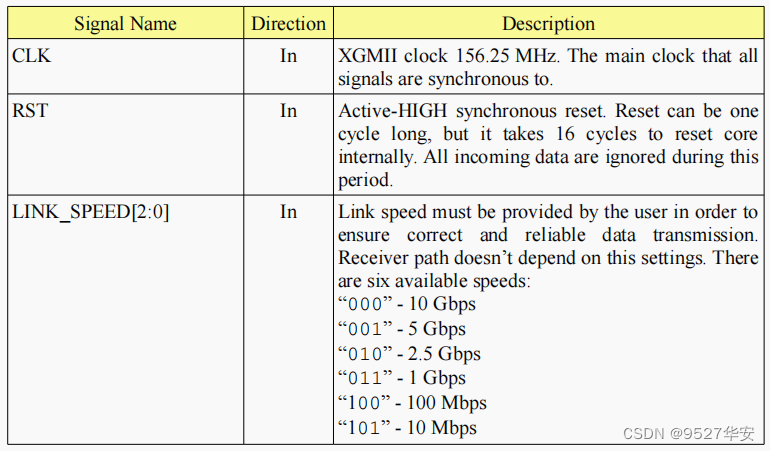

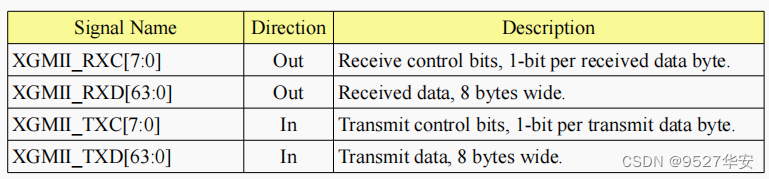

- XGMII接口描述

- 4、vivado工程详解

- 10G-UDP协议栈

- 10G Ethernet PCS/PMA IP核

- 5、上板调试验证并演示

- 6、福利:工程代码的获取

1、前言

目前网上的fpga实现udp基本生态如下:

1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是废物,在实际项目中不会用这样的代码,试想,多机互联,出现了问题,你的网卡都不带ping功能,连基本的问题排查机制都不具备,这样的代码谁敢用?

2:带ping功能的udp收发器,代码优秀也好用,但基本不开源,不会提供源码给你,这样的代码也有不足,那就是出了问题不知道怎么排查,毕竟你没有源码,无可奈何;

3:使用了Xilinx的Tri Mode Ethernet MAC三速网IP实现,这样的代码也很优秀,但还是那个问题,没有源码,且三速网IP需要licence,三速网IP实现了rgmii到gmii再到axis的转换;

4:使用FPGA的GTX资源利用SFP光口实现UDP,通信,这种方案不需要外接网络变压器即可完成,本方案就是此种设计;

本设计使用纯VHDL代码实现的UDP协议栈实现UDP通信的MAC层设计,调用Xilinx官方的10G Ethernet Subsystem IP核实现了网络变压器的功能,从而实现无需外挂网络芯片即可实现UDP通信的方案,轻松实现时下热门的10G万兆网通信;进行10G UDP数据回环测试;本例程使用的10G UDP该协议栈带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;本设计通过数据的回环收发,在电脑端使用网络调试助手进行UDP收发验证;

本设计链接1路SFP光口,配置为UDP服务器,本设计经过反复大量测试稳定可靠,可在项目中直接移植使用,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字通信领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2、我这里已有的UDP方案

目前我这里有如下几种UDP方案和应用实例:

我的博客主页有个FPGA以太网通信专栏,专栏是免费的,里面有很多FPGA实现的UDP应用,既有常规千兆网也有万兆网方案,对网络通信有需求的兄弟可以去看看:直接点击前往

3、详细设计方案

本 10G-UDP 协议栈功能和性能描述

1:为了更加收敛的时序和更加严谨的逻辑,代码采用纯VHDL语言编写;

2:由于使用了 xpm_fifo_sync 源语,目前只能在Xilinx平台使用;若需在Altera、国产FPGA等平台移植,将xpm_fifo_sync源语替换为所在平台的 fifo 源语或者 fifo ip 即可;

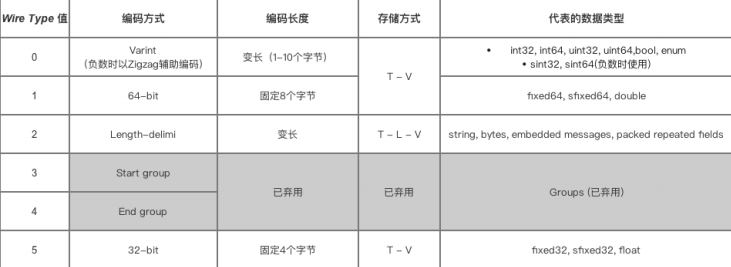

3:基于 UDP 协议的通信协议,全带宽高达 10 Gbps 的速度,且经过反复测试不丢失数据包;

4:UDP 数据包缓冲 fifo 深度可调,也就是说在满足 UDP 数据包最大边界的情况下可自由配置 UDP 数据包大小;

5:基于 IPv4,IP广播,不支持碎片整理;不支持 IPv6;

6:静态ARP,不带ping功能;

7:XGMII 接口,156.25 MHz 时钟 64bit 数据位宽;可与 Xilinx 的 10G Ethernet 连接使用;

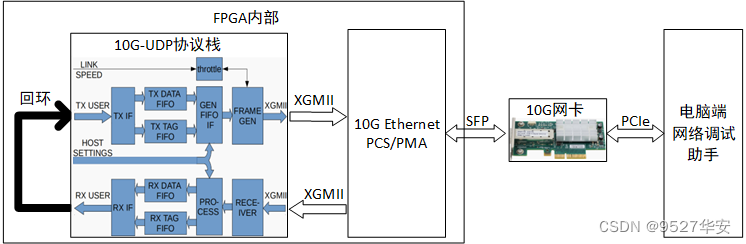

本 10G-UDP 协议栈设计框图

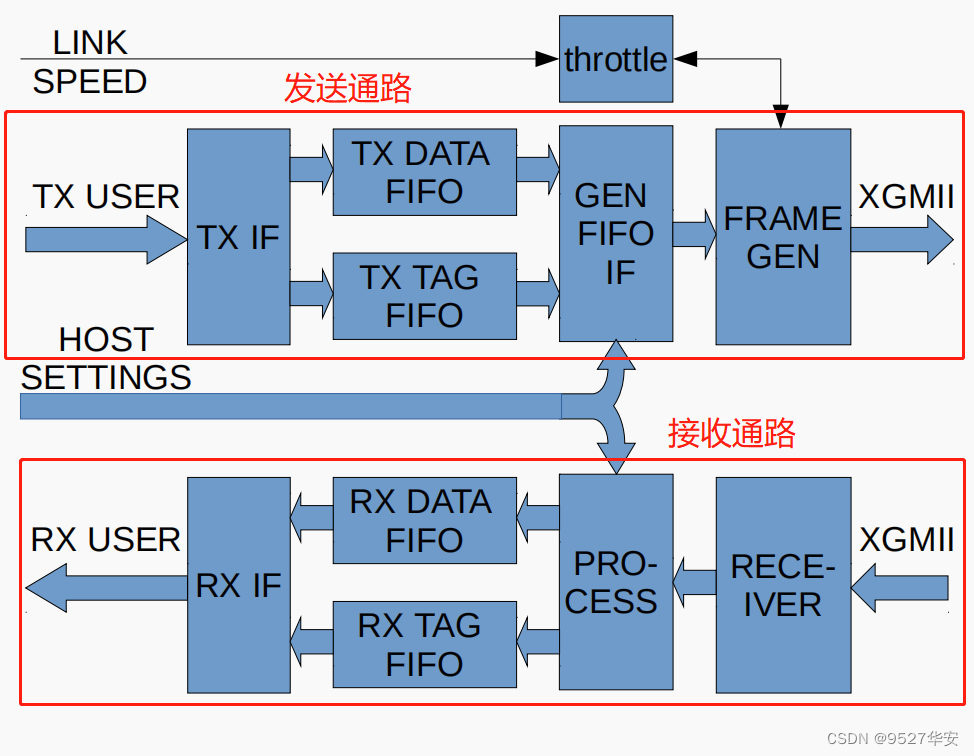

10G-UDP协议栈由接收和发送两大功能模块组成,模块具体框图如下:

顶层文件拖入vivado的Block Design后以IP的形式更加直观的体现10G-UDP协议栈的接口关系,如下:

用户发送AXIS接口描述

时钟、复位和HOST-SETTINGS接口为固定接口,其余都是独立接口,其中接收和发送的用户接口为自定义具有握手机制的接口,与MAC层的数据接口为XGMII接口;

HOST-SETTINGS接口主要配置主从机的IP地址、MAC地址、子网掩码等,这些配置信息将传递到UDP的接收和发送通路逻辑中去;

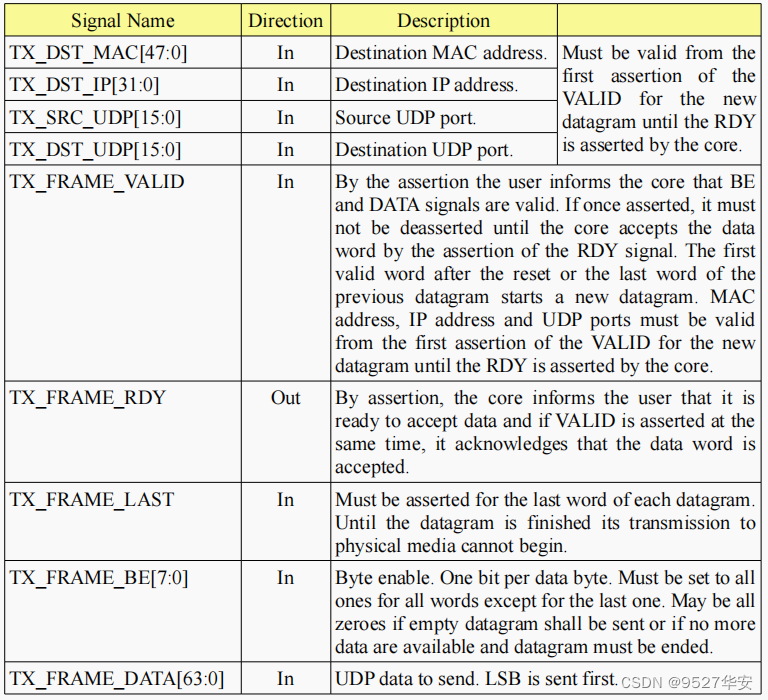

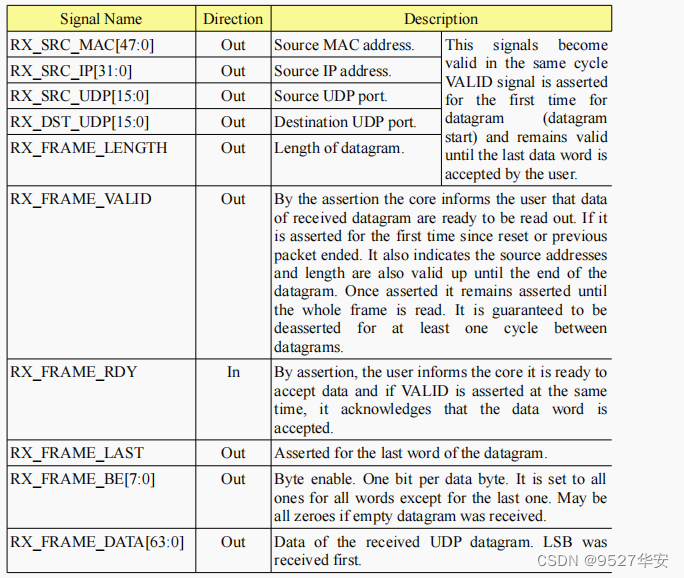

用户发送接口功能描述如下:

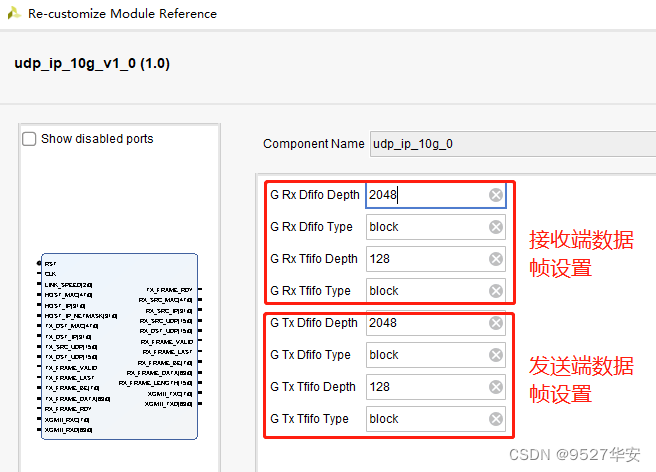

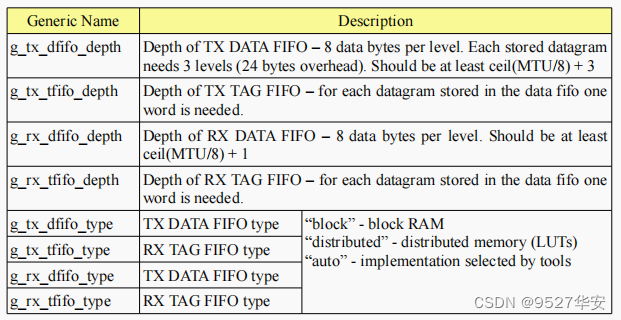

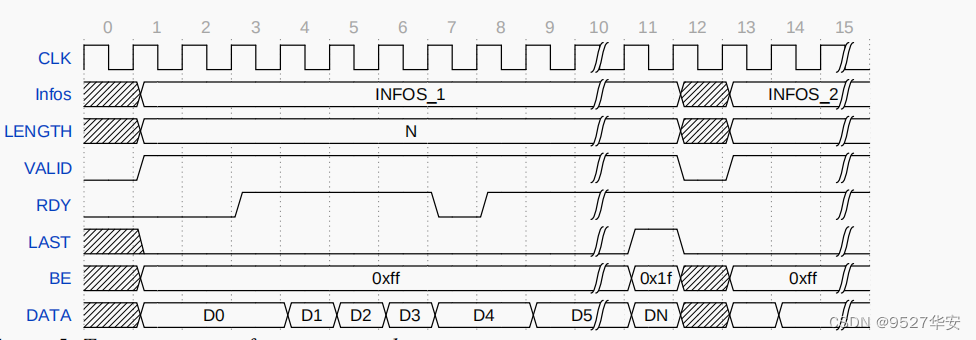

根据上表可知,用户数据在TX_FRAME_VALID和TX_FRAME_RDY都为高时被采集,也就是前面说的握手机制,TX_FRAME_LAST表示一帧数据的结束,TX_FRAME_BE[7:0]表示8个字节数据的使能,TX_FRAME_DATA[63:0]是发送的数据,这个接口其实就是去掉了TUSER的AXIS接口,这里的数据是以帧的形式传输的,那么一帧数据到底包括多少个TX_FRAME_DATA[63:0]呢?帧数据大小的设置是通过参数设置的,如下:

这些参数的具体释义如下:

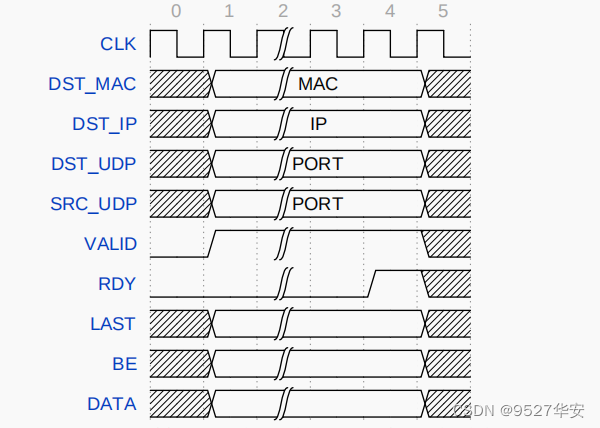

对于FPGA开发者而言,最关注的莫非于用户接口的时序,某种意义而言,看懂了用户时序,或者给出了用户时序图,我们就可以写出对接的时序,就能设计我们想要的功能,对于发送端的时序而言主要由两个,一个是数据发送前的UDP/IP的基本参数的输入,HOST-SETTINGS接口主要配置主从机的IP地址、MAC地址、子网掩码等,才发送时序下的载入如下:

可以看到,第1个时钟到第4个时钟之间虽然IP、MAC等参数虽已载入总线,但TX_FRAME_VALID和TX_FRAME_RDY并未握手成功,所以为无效数据,在第5个时钟被采集;

数据传输时的用户发送时序如下:

用户接收AXIS接口描述

时钟、复位和HOST-SETTINGS接口为固定接口,其余都是独立接口,其中接收和发送的用户接口为自定义具有握手机制的接口,与MAC层的数据接口为XGMII接口;

HOST-SETTINGS接口主要配置主从机的IP地址、MAC地址、子网掩码等,这些配置信息将传递到UDP的接收和发送通路逻辑中去;

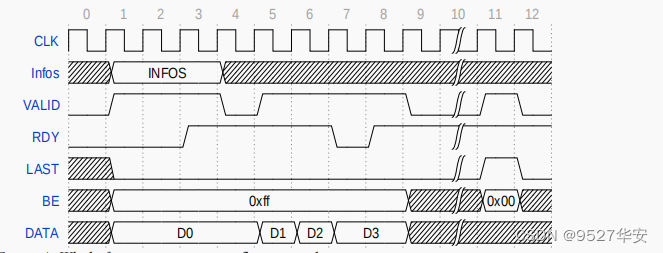

用户接收接口和发送接口差不多,所以不再详细描述,参考前面的发送部分描述即可,这里只给出时序图;

用户接收接口功能描述如下:

控制接口描述

本 10G UDP 协议栈留有控制接口,可以通过控制接口控制不同的速率,此外,还可以配置如下:

HOST-SETTINGS接口主要配置主从机的IP地址、MAC地址、子网掩码等,这些配置信息将传递到UDP的接收和发送通路逻辑中去,如下:

XGMII接口描述

XGMII接口很简单,和10G Ethernet IP的XGMII接口对接,如下:

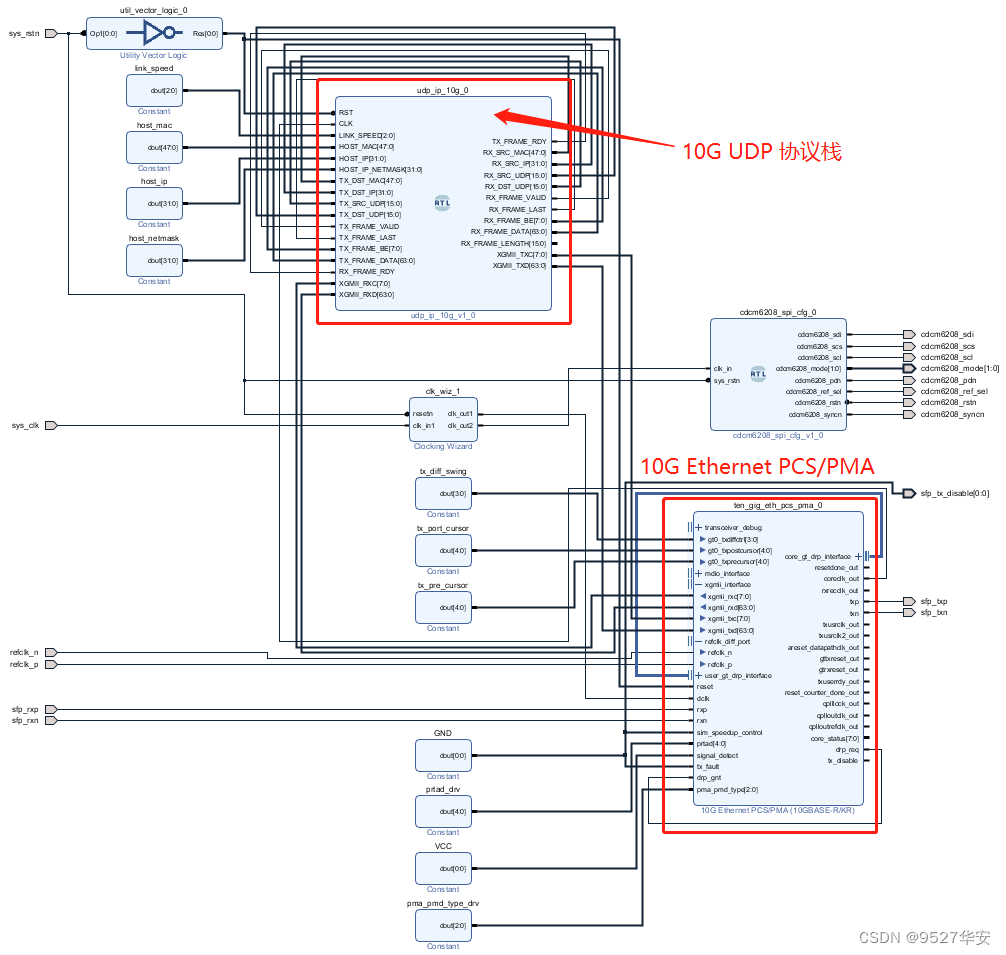

4、vivado工程详解

开发板FPGA型号:Xilinx–xc7k325tffg676-2;

开发环境:vivado2019.1;

输入/输出:SFP光口;

网卡速度:10G;

测试项:UDP数据回环;

工程整体架构、模块架构、硬件连接如下:

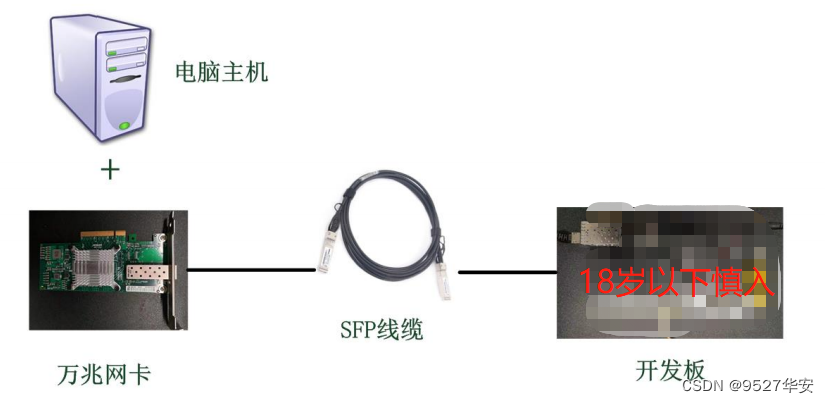

10G-UDP协议栈工程以10G-UDP协议栈为核心,调用Xilinx官方的10G Ethernet PCS/PMA IP核,在无需网络变压器芯片的情况下,利用Xilinx的GTX资源实现了物理层的PCS和PMA功能,最后通过SFP光口收发UDP数据,SFP接头的光纤线缆连接10G网卡,网卡通过PCIe插在电脑主机的主板上,电脑端打开网络调试助手实现和FPGA的网络数据UDP包的收发,FPGA端的10G-UDP协议栈将收发回环起来,这样就形成了UDP数据的回环收发;

对应的,vivado工程的Block Design如下:

10G-UDP协议栈

将 10G-UDP 协议栈的用于TX和用户RX接口对接起来形成回环,同时设置FIFO深度和RAM类型,还需设置主机IP地址、MAC地址、子网掩码等信息,系统上电后,10G-UDP协议栈将自动实现数据的回环收发;10G-UDP协议栈配置如下:

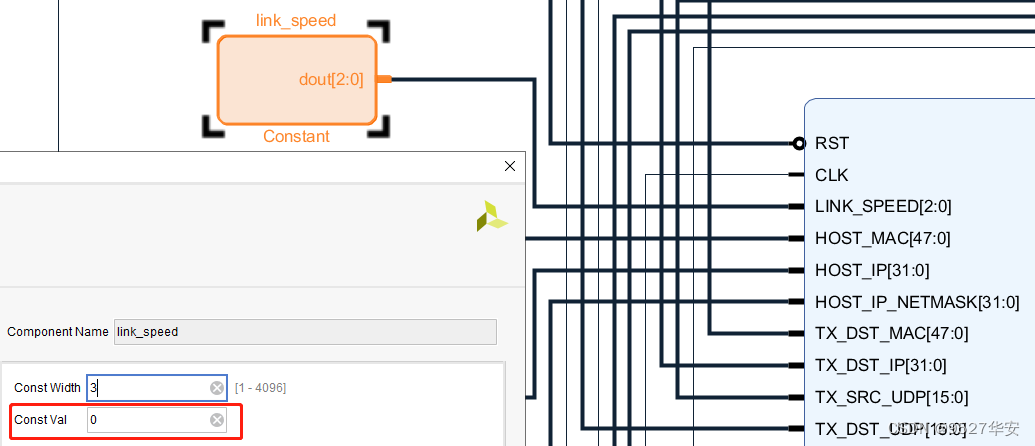

1:设置链路速率为 10Gbps:

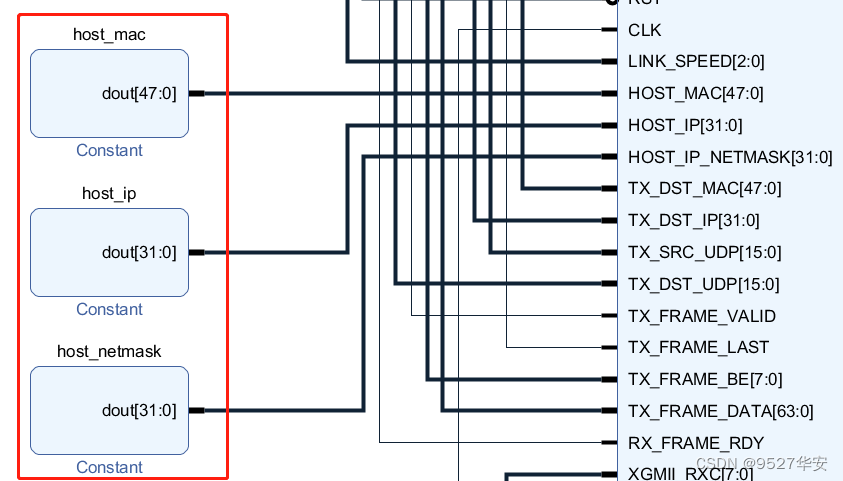

2:设置评估板 MAC 地址为 00-23-20-21-22-23,IP 地址为 192.168.0.25,子网掩码为255.255.254.0;

10G Ethernet PCS/PMA IP核

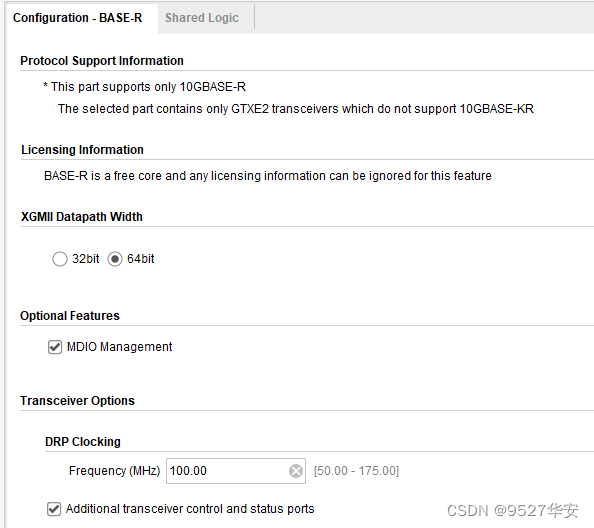

本案例使用 10G Ethernet PCS/PMA IP 核实现物理层(PCS 与 PMA)功能;10G Ethernet PCS/PMA IP 核开发文档为Xilinx 官方参考文档《pg068-ten-gig-eth-pcs-pma》,具体配置说明如下:

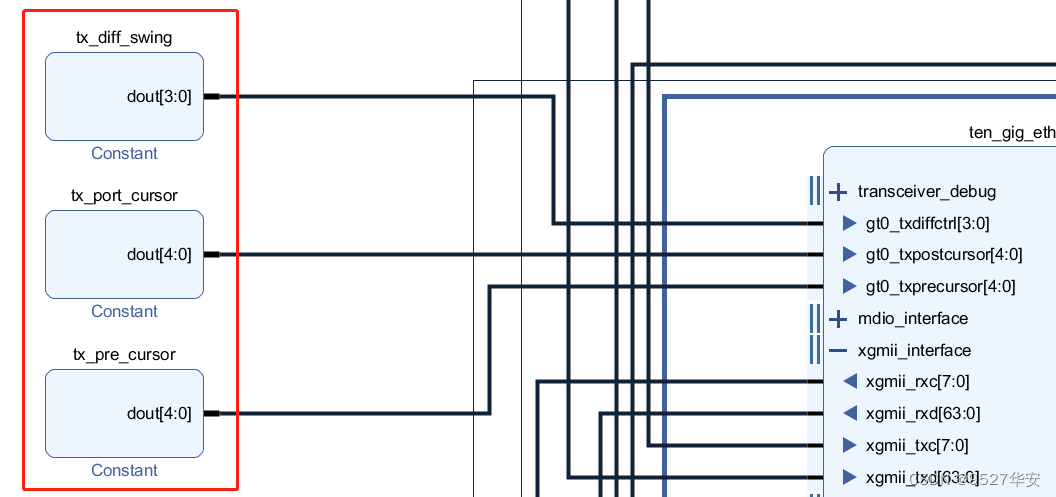

1:选中"Additional transceiver control and status ports",新增并设置 TX Pre-Cursor、TX Post-Cursor 和 TX Diff Swing 选项值,以提高 GTX 信号传输质量。其中 tx_pre_cursor设置为 0x15、tx_pre_cursor 设置为 0xA、tx_diff_swing 设置为 0x9;

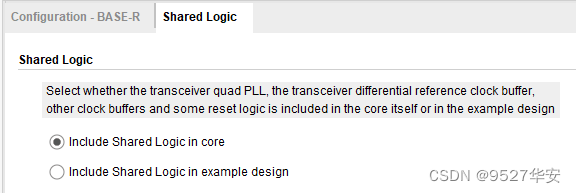

2:勾选 Shared Logic 的"Include Shared Logic in core",配置 10G Ethernet PCS/PMA IP核包含共享逻辑;

工程代码架构如下:

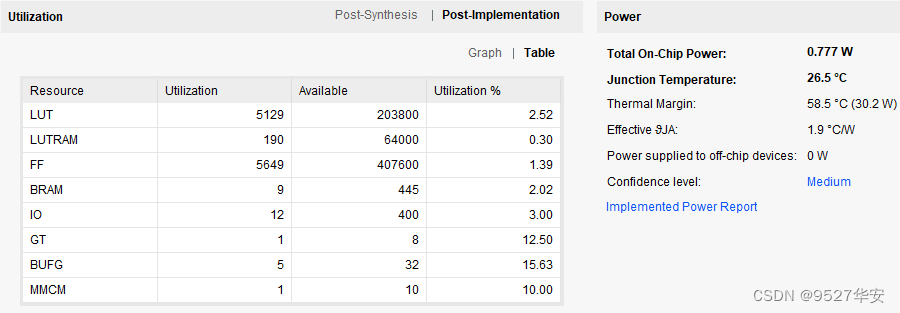

综合编译后的FPGA资源消耗和功耗预估如下:

5、上板调试验证并演示

本实验需要用户自己准备 10G 网卡,插到电脑主板上。下图为我在某鱼上买的二手货。。。

连接方式如下:

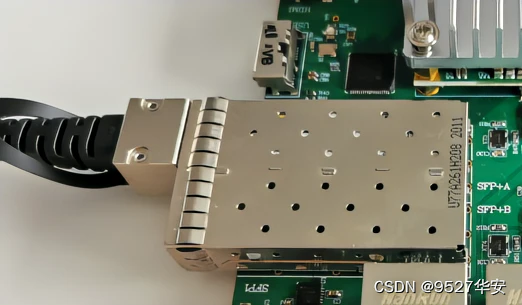

开发板侧SFP连接如下:

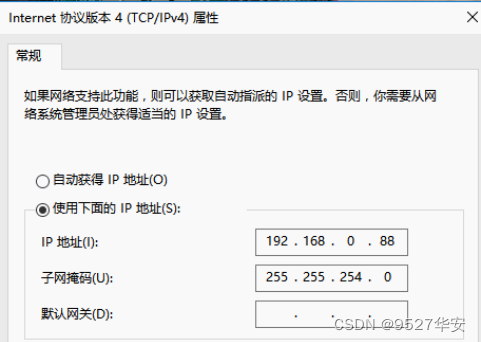

FPGA开发板 IP 地址已通过10G-UDP协议栈模块配置为 192.168.0.25。请设置 PC 机 IP 地址与FPGA开发板 IP 地址处于同一网段。此处将 PC 机 IP 地址设置为 192.168.0.88,子网掩码设为255.255.254.0;

请下载bit运行程序,此时 PC 机将会识别网络连接状态为 10Gbps;

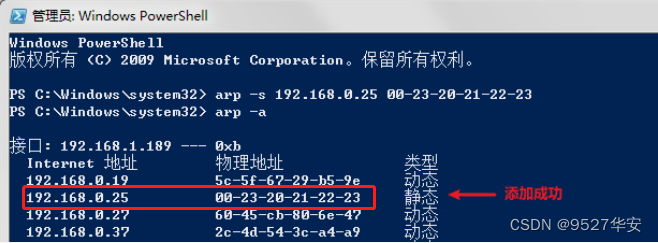

由于10G-UDP协议栈模块不支持 动态ARP(Address Resolution Protocol)地址解析协议,因此需通过添加FPGA开发板 IP 地址和 MAC 地址的静态映射关系。请以管理员身份打开 Windows PowerShell或者CMD,并执行如下命令;

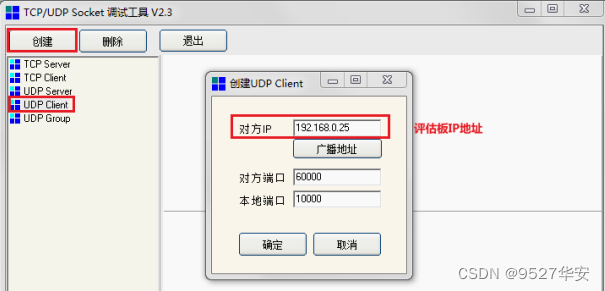

双击打开网络调试工具 SocketTool_NoAD.exe,在弹出的界面中点击“UDP Client -> 创建”,在“对方 IP”中输入FPGA开发板 IP 地址,再点击确定;网络调试工具 SocketTool_NoAD.exe已放在资料包中,你们也可以使用其他的网络调试工具;

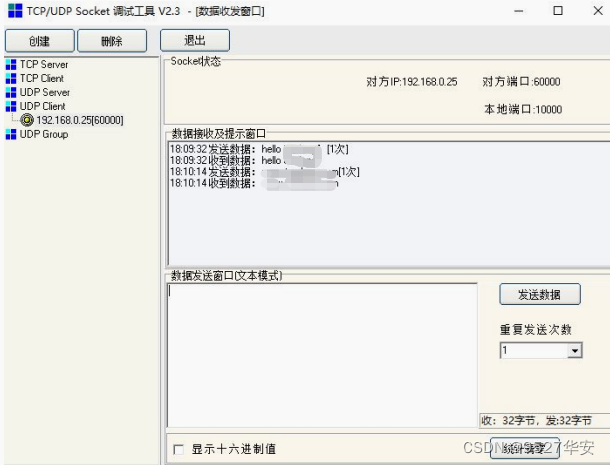

在“数据发送窗口”中输入需发送至评估板的数据,再点击“发送数据”。“数据接收及提示窗口”中将打印由 PC 机发送至FPGA开发板 ,以及由评估板发送至 PC 机的数据;

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

![【PWN · ret2libc】[2021 鹤城杯]babyof](https://img-blog.csdnimg.cn/6c95d5c7027a44daade842236b7345c9.png)