此文章只用于教程开发笔记,不做过多的废话介绍。

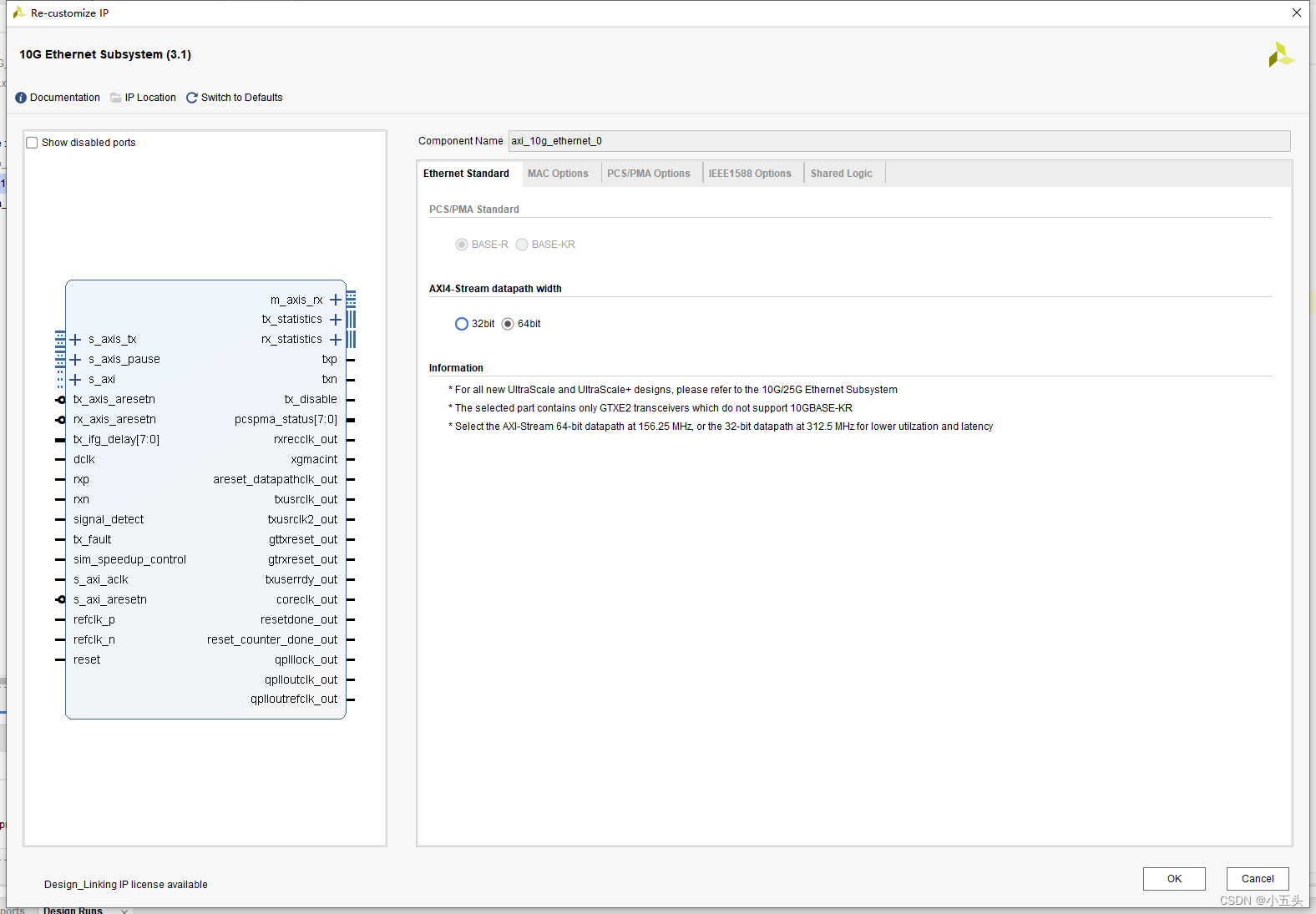

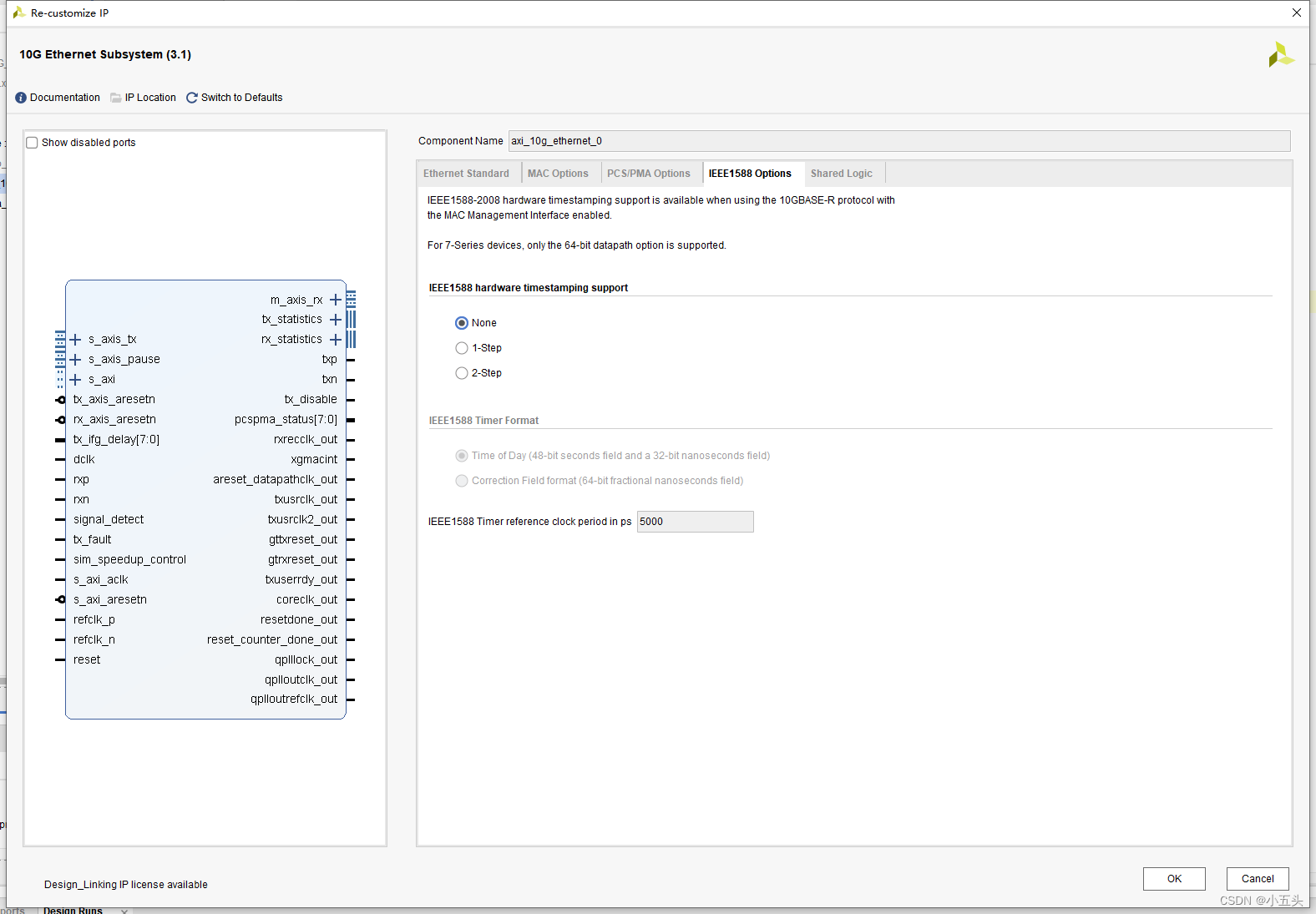

IP核的建立

此选项不进行共享时钟逻辑。优点接口少好操作,缺点只可以建立一个IP核。(我有一篇文章介绍了如何进行多个核互联)传送门:FPGA光纤Aurora_8B_10B_fpga aurora的实际带宽-CSDN博客

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

axi_10g_ethernet_0 your_instance_name (

.tx_axis_aresetn(tx_axis_aresetn), // 复位 。 需拉低一段时间

.rx_axis_aresetn(rx_axis_aresetn), // 复位 。 需拉低一段时间

.tx_ifg_delay(tx_ifg_delay), // input wire [7 : 0] tx_ifg_delay

.dclk(dclk), // DRP 时钟

.txp(txp), // 光口

.txn(txn), // 光口

.rxp(rxp), // 光口

.rxn(rxn), // 光口

.signal_detect(signal_detect), // input wire signal_detect

.tx_fault(tx_fault), // 检测光模块 状态信号

.tx_disable(tx_disable), // 连接光模块的控制

.pcspma_status(pcspma_status), // output wire [7 : 0] pcspma_status

.sim_speedup_control(sim_speedup_control), // 使用此信号,可缩短计算时间1 用于仿真

.rxrecclk_out(rxrecclk_out), // 时钟

.s_axi_aclk(s_axi_aclk), // input wire s_axi_aclk

.s_axi_aresetn(s_axi_aresetn), // input wire s_axi_aresetn

.xgmacint(xgmacint), // output wire xgmacint

.areset_datapathclk_out(areset_datapathclk_out), // output wire areset_datapathclk_out

.txusrclk_out(txusrclk_out), // output wire txusrclk_out

.txusrclk2_out(txusrclk2_out), // output wire txusrclk2_out

.gttxreset_out(gttxreset_out), // output wire gttxreset_out

.gtrxreset_out(gtrxreset_out), // output wire gtrxreset_out

.txuserrdy_out(txuserrdy_out), // output wire txuserrdy_out

.coreclk_out(coreclk_out), // output wire coreclk_out

.resetdone_out(resetdone_out), // output wire resetdone_out

.reset_counter_done_out(reset_counter_done_out), // output wire reset_counter_done_out

.qplllock_out(qplllock_out), // output wire qplllock_out

.qplloutclk_out(qplloutclk_out), // output wire qplloutclk_out

.qplloutrefclk_out(qplloutrefclk_out), // output wire qplloutrefclk_out

.refclk_p(refclk_p), // input wire refclk_p

.refclk_n(refclk_n), // input wire refclk_n

.reset(reset), // input wire reset

.s_axi_araddr(s_axi_araddr), // input wire [10 : 0] s_axi_araddr

.s_axi_arready(s_axi_arready), // output wire s_axi_arready

.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid

.s_axi_awaddr(s_axi_awaddr), // input wire [10 : 0] s_axi_awaddr

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

.s_axi_bready(s_axi_bready), // input wire s_axi_bready

.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp

.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

.s_axi_rready(s_axi_rready), // input wire s_axi_rready

.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp

.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

//axis_tx数据接口 发送

.s_axis_tx_tdata(s_axis_tx_tdata), // input wire [63 : 0] s_axis_tx_tdata

.s_axis_tx_tkeep(s_axis_tx_tkeep), // input wire [7 : 0] s_axis_tx_tkeep

.s_axis_tx_tlast(s_axis_tx_tlast), // input wire s_axis_tx_tlast

.s_axis_tx_tready(s_axis_tx_tready), // output wire s_axis_tx_tready

.s_axis_tx_tuser(s_axis_tx_tuser), // input wire [0 : 0] s_axis_tx_tuser

.s_axis_tx_tvalid(s_axis_tx_tvalid), // input wire s_axis_tx_tvalid

.s_axis_pause_tdata(s_axis_pause_tdata), // input wire [15 : 0] s_axis_pause_tdata

.s_axis_pause_tvalid(s_axis_pause_tvalid), // input wire s_axis_pause_tvalid

//axis_rx数据接口 接收

.m_axis_rx_tdata(m_axis_rx_tdata), // output wire [63 : 0] m_axis_rx_tdata

.m_axis_rx_tkeep(m_axis_rx_tkeep), // output wire [7 : 0] m_axis_rx_tkeep

.m_axis_rx_tlast(m_axis_rx_tlast), // output wire m_axis_rx_tlast

.m_axis_rx_tuser(m_axis_rx_tuser), // output wire m_axis_rx_tuser

.m_axis_rx_tvalid(m_axis_rx_tvalid), // output wire m_axis_rx_tvalid

.tx_statistics_valid(tx_statistics_valid), // 数据有效信号

.tx_statistics_vector(tx_statistics_vector), // 状态标志信号

.rx_statistics_valid(rx_statistics_valid), // 数据有效信号

.rx_statistics_vector(rx_statistics_vector) // 状态标志信号

);顶层接口定义

module 10G_ethernet(

input sys_clk_100m ,//板卡的系统时钟

input refclk_n_0 ,//光口时钟

input refclk_p_0 ,

input rxn_0 ,//光口接收

input rxp_0 ,

output txp_0 ,//光口发送

output txn_0 ,

output led ,//工作状态指示信号

output tx_dis //通道开启信号

);功能验证

需要准备工具:10G网卡一个(PCIE接口)、支持10G的光模块两个、光纤线缆一对。

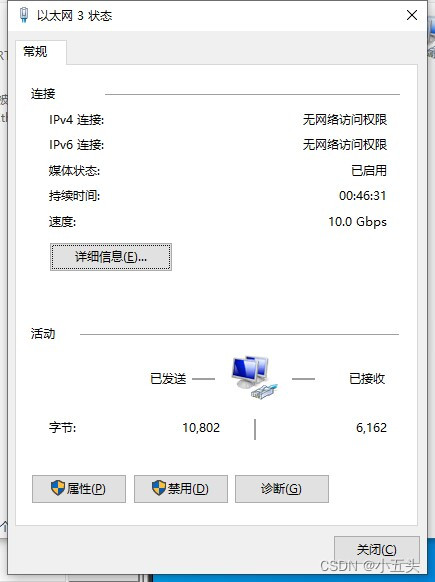

程序下载完成后,10G网卡灯亮起,证明与10G Ethernet Subsystem 核link成功,这时可查看电脑的网络现实状态。

配置好IP地址后,可使用网络传输助手进行通讯。

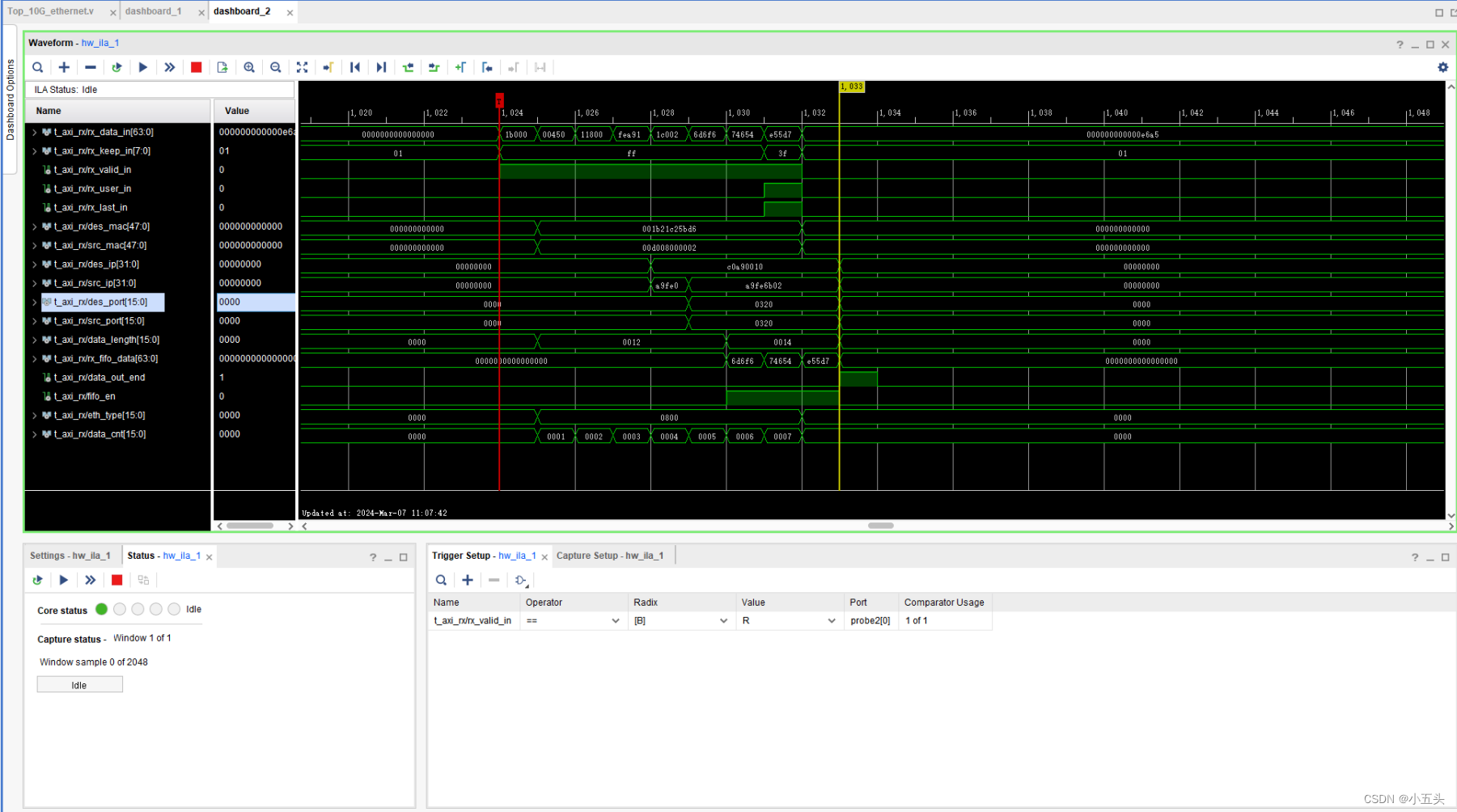

Des_ip : c0a900010 发送端主机的IP地址 192.168.0.16

Des_mac : 发送端主机的MAC地址 00-1b-21-c2-5b-d6

Des_port : 源端口号 0800

Eth_type : 长度类型

Src_ip :a9fe6b02 源ip 开发板ip地址 169.254.107.2

Src_mac :源mac地址 开发板mac地址 00-d0-08-00-00-02

Scr_port :目的端口号 与源端口号保持一致即可

Rx_last_in :表示一个数据包的结束

Rx_user_in:0表示接收的数据包坏的 , 1表示接收的数据包好的

Rx_valid_in :数据有效信号

Fifo_en :数据有效信号

Rx_data_in :数据信号

Rx_fifo_data :数据信号